В настоящей статье рассматривается буферизированный синхронный последовательный интерфейс Queued SPI (QSPI). Приводятся основные технические характеристики данного интерфейса и его особенности, рассматривается структурная схема модуля QSPI и дается ее краткое описание, рассматривается сигнальный уровень, а также приводится сравнительный анализ SPI и QSPI. А также представлены примеры микросхем с использованием данного интерфейса.

Введение

Интерфейс QSPI является полно дуплексным синхронным последовательным интерфейсом, предназначенным для связи с периферийными устройствами и другими вычислительными устройствами. Основная идея QSPI заключается в том, чтобы минимизировать участие центрального процессора в управлении информационным обменом между ведущим и ведомым.

Основные технические характеристики

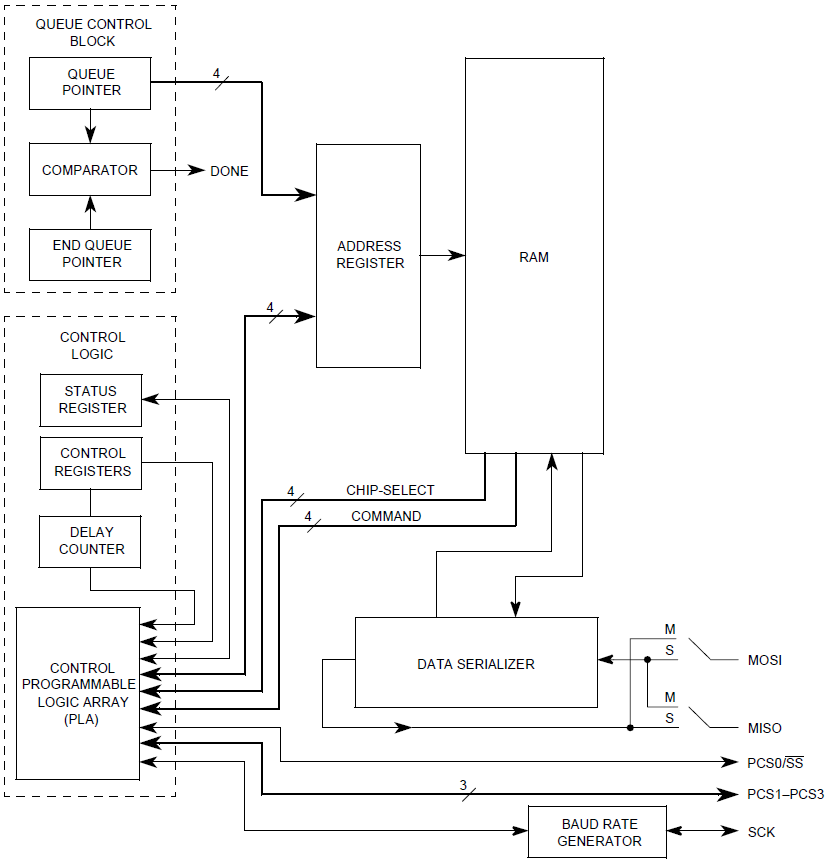

Структурная схема модуля интерфейса QSPI приведена на рисунке 1.

В состав модуля QSPI входят четыре регистра управления (см. Рисунок 1, Control registers), один регистр статуса и блок статического оперативного запоминающего устройства (СОЗУ) объемом 80 байт (объем памяти зависит реализации). Центральный процессор имеет полный доступ ко всем регистрам и ОЗУ модуля QSPI. За более подробным описанием программной модели модуля QSPI следует обратиться к описанию конкретного типа микроконтроллера (МК) или процессора.

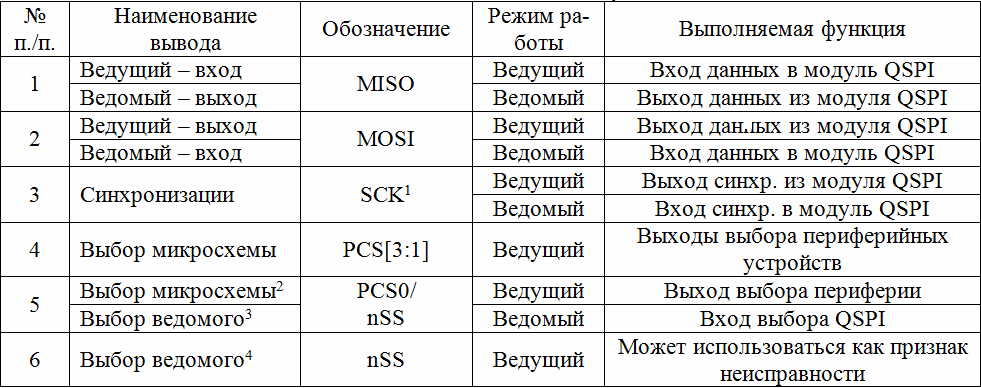

Модуль интерфейса QSPI имеет 7 сигнальных линий: MISO, MOSI, SCK, PCS [3:0]. Линии PCS [3:0] эти 4 сигнала обеспечивают модулю интерфейса QSPI выбор периферийных устройств. Сигнал nSS/PCS0 является двунаправленным, но может быть настроен на ввод в режиме ведомого. По линии SCK передается сигнал синхронизации, он может быть настроен в режиме ведущего как выход, а в режиме ведомого как вход. По линии MISO передаются данные, в режиме ведущего работает на ввод данных в модуль QSPI, а в режиме ведомого на вывод данных. Соответственно линия MOSI наоборот. Функциональное назначение внешних сигнальных линий и соответствующие им режимы работы приведены в таблице 1.

Таблица 1 – Внешние линии ввода/вывода модуля QSPI

Примечание:

1. Все выводы QSPI (кроме SCK) могут быть использованы как линии общего назначения I/O, если они не используются интерфейсом QSPI.

2. Вывод PCS0 работает как выход, когда модуль QSPI работает в режиме ведущего.

3. Вывод nSS работает как вход, когда модуль QSPI работает в режиме ведомого.

4. Вывод nSS работает как вход, когда модуль QSPI работает в режиме ведущего, данная возможность полезна в системах с множеством ведущих.

Особенности интерфейса QSPI

Особенности QSPI:

– возможность заранее запрограммировать до 16 передач;

– возможность запрограммировать до 4-х линий выбора микросхем, что позволяет подключать до 16 микросхем;

– режим автоматического сканирования подключенной периферии;

– программируемая длина передачи от 8 до 16 бит включительно;

– программируемая задержка передачи от 1 мкс до 0,5 мс;

– программируемый указатель буфера;

– возможность непрерывной передачи до 256 бит (32 байта или 16 слов).

Программируемый буфер позволяет QSPI выполнять до 16 последовательных передач без вмешательства центрального процессора. Каждая передача соответствует записи, содержащей в буфере всю необходимую информацию для самостоятельного завершения информационного обмена. Эта уникальная особенность значительно снижает загрузку центрального процессора, что приводит к увеличению производительности системы в целом.

Наличие 4-х программируемых линий выбора микросхем позволяет осуществлять доступ к 16 независимым периферийным устройствам, но для этого по-требуется дешифратор. Однако четыре периферийных устройства могут работать при помощи прямого подключения. Данная функция значительно упрощает взаимодействие двух или более периферийных устройств, что также устраняет необходимость участия центрального процессора.

Режим автоматического сканирования подключенной периферии, позволяет непрерывно и повторно выполнять запись в буфер. Вновь записанные данные заменяют более поздние, таким образом, подключенные периферийные устройства отображается в памяти центрального процессора.

Количество битов последовательной передачи программируется от 8 до 16 бит включительно. Так, например, 10 битный режим может быть использован для связи с внешним 10 битным АЦП. Данная возможность упрощает взаимодействие с последовательными периферийными устройствами, которые требуют различных длин данных.

Программируемая задержка передачи может быть установлена в пределах от 1 до 500 мкс. Как и в предыдущем случае, данная возможность может быть использована при работе с АЦП, где требуется время на преобразование сигнала. Возможность программирования задержки передачи также упрощает работу с последовательной периферией.

Модуль интерфейса QSPI имеет указатель, который определяет местоположение буфера. Таким образом, возможность сегментации буфера позволяет предусматривать выполнение нескольких задач.

Режим непрерывной передачи позволяет пользователю передавать/принимать непрерывный поток данных от периферийного устройства. Минимальная длина 8 бит, а максимальная 256 бит, которая может быть передана непрерывно и без вмешательства центрального процессора. Более длинные транзакции также возможны, однако в данном случае потребуется минимальное вмешательство процессора.

Где применяется QSPI?

Интерфейс QSPI, применяет фирма «Freescale» в своих разработках МК серии MC68332, а также в АЦП серий MC145050 и MC145040, но это все достаточно древние изделия. Из более новых разработок той же фирмы можно выделить МК серии Cold Fire, например MCF52223, MCF52221 и другие. Фирма «Analog Devices» применяет интерфейс QSPI в АЦП, например AD7887, AD7888, AD7452, AD7853 и других.

Кратко о SPI?

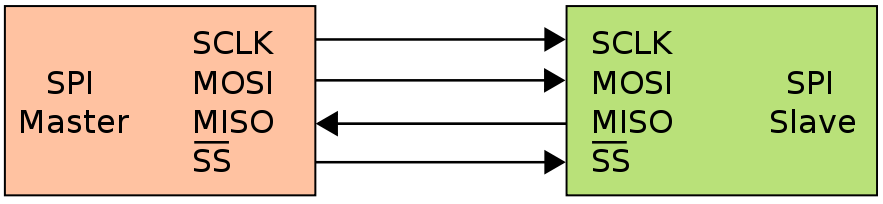

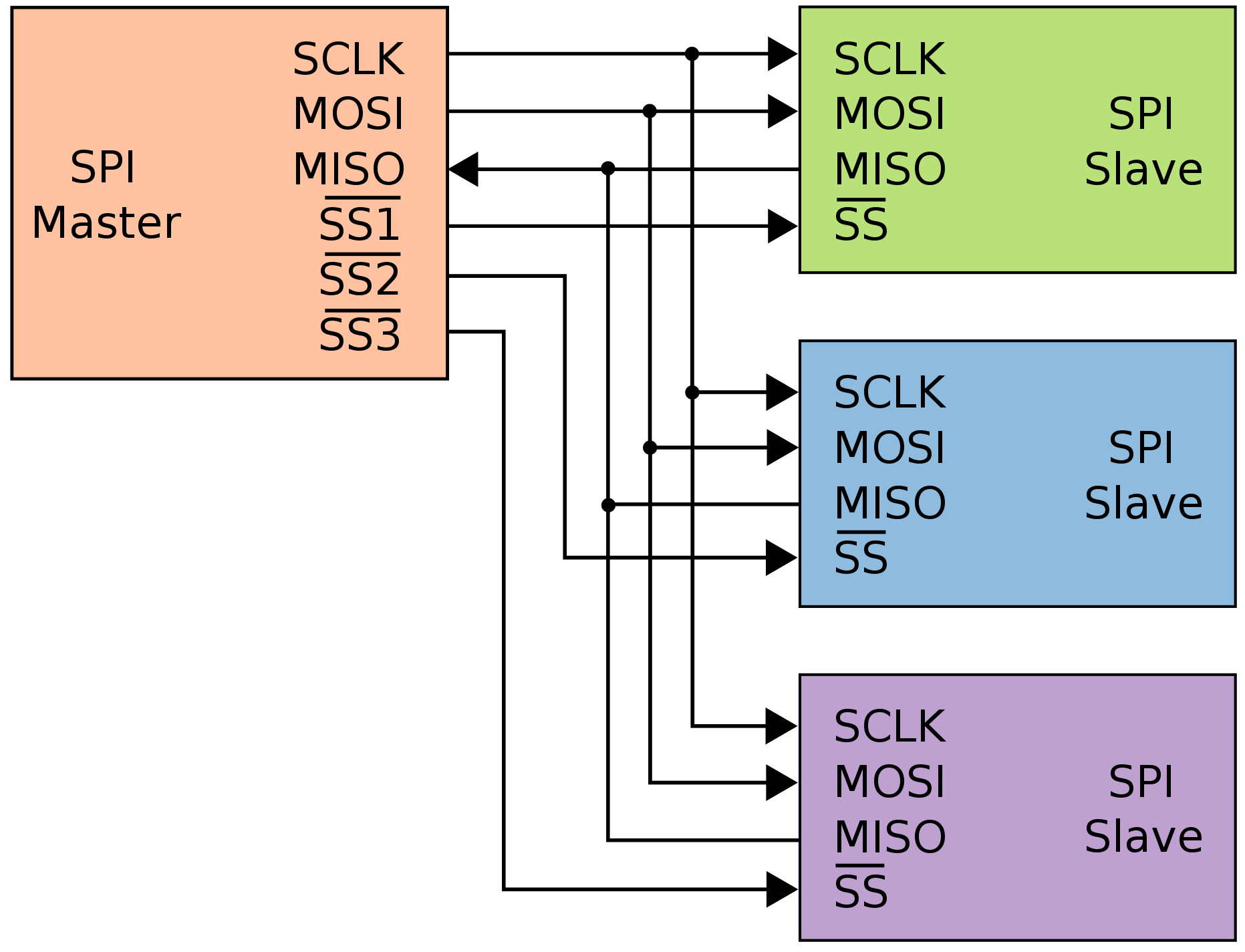

Интерфейс QSPI совместим с интерфейсом SPI, поэтому функционирование этих двух интерфейсов в значительной мере схожи. Или, другими словами интерфейс QSPI это просто расширение шины SPI. Для последующего сравнительного анализа интерфейсов QSPI и SPI приведем типовые структурные схемы связей SPI мастера с одним и несколькими ведомыми, которые приведены на рисунках 1 и 2 соответственно.

Особенности интерфейса SPI приведены ниже:

– полный дуплекс, трех проводной интерфейс, синхронный;

– полу дуплекс, двух проводной интерфейс, синхронный;

– режим ведомого или ведущего;

– программируемый бит мастера;

– программируемая фаза сигнала синхронизации;

– флаг прерывания окончания передачи;

– флаг неисправности в режиме ведущий-ведущий;

– простота взаимодействия с такими устройствами как: АЦП, ЦАП, ЭСППЗУ, и другими.

Так чем же отличается QSPI от SPI?

Рассмотрев основные технические характеристики интерфейсов QSPI и SPI можно сделать вывод, что интерфейс QSPI отличается наличием буфера данных объемом 32 байта, а также в нем предусмотрена аппаратная возможность подключения до 16 периферийных устройств. В случае с SPI (см. рисунок 3) также можно управлять 16-ю и даже более устройствами, что в принципе ограниченно лишь количеством линий общего назначения конкретного типа микроконтроллера или процессора, однако в этом случае реализация механизма переключения ложиться на встроенное программное обеспечение, то есть на сам процессор. Еще одной отличительной особенностью SPI от QSPI является возможность изменения длины передаваемых данных от 8 до 16 бит, что придает элемент адаптивности QSPI (хотя во многих современных микроконтроллерах эта опция уже присутствует). Таким образом, приведенные выше преимущества QSPI позволяют центральному процессору сконцентрироваться на своих основных задачах (как правило, задачи вычисления) и не тратить свое время на управление информационным обменом с периферийными устройствами.