В предлагаемой статье рассматривается новая разработка ОАО «Интеграл», микросхема сегнетоэлектрической оперативной памяти (Ferroelectric RAM, FeRAM или FRAM) 1666РЕ014. Приводятся электрические характеристики микросхемы, габаритные и установочные размеры микросхемы, приводятся параметры надежности, даются рекомендации по применению и эксплуатации данных микросхем, а также приводятся значения внешних воздействующих факторов. Зарубежным аналогом 1666РЕ014 является микросхема FM28V100, производства американской фирмы «Ramtron» (сейчас выкуплена другой американской компанией Cypress Semiconductor).

Микросхема 1666РЕ014 представляет собой сегнетоэлектрическое энергонезависимое ОЗУ информационной емкостью 1 Мбит с организацией 128К×8 бит.

При работе микросхема 1666РЕ014 считывает и записывает данные подобно стандартному СОЗУ и может быть использована в качестве прямой замены стандартного СОЗУ. Циклы чтения и записи могут быть синхронизированы переключением входа сигнала разрешения, либо изменением адреса. Микросхема является энергонезависимой благодаря процессу сегнетоэлектрического запоминания и обеспечивает сохранение данных после отключения питания.

Микросхема 1666РЕ014 предназначена для построения блоков оперативной памяти вычислительных систем специального назначения.

Условное обозначение и функциональное назначение микросхемы приведено в таблице 1. Пример обозначения микросхемы при заказе: «Микросхема 1666РЕ014 – АЕЯР.431220.981 ТУ».

Таблица 1 - Обозначение и функциональное назначение микросхемы

| Условное обозначение микросхемы | Основное функциональное назначение |

|---|---|

| Энергонезависимое оперативное запоминающее устройство (128К×8) бит. |

Краткие технические характеристики 1666РЕ014 представлены в таблице 2.

Таблица 2 – Краткие технические характеристики 1666РЕ014

| Наименование параметра | Норма параметра |

|---|---|

| Напряжение питания, В | |

| Динамический ток потребления, мА | |

| Ток потребления в режиме хранения, мкА | |

| Организация накопителя | |

| Количество циклов чтение/запись | |

| Работа в страничном режиме с частотой, МГц | |

| Время выбора, нс | |

| Время цикла, нс | |

| Температурный диапазон, °С |

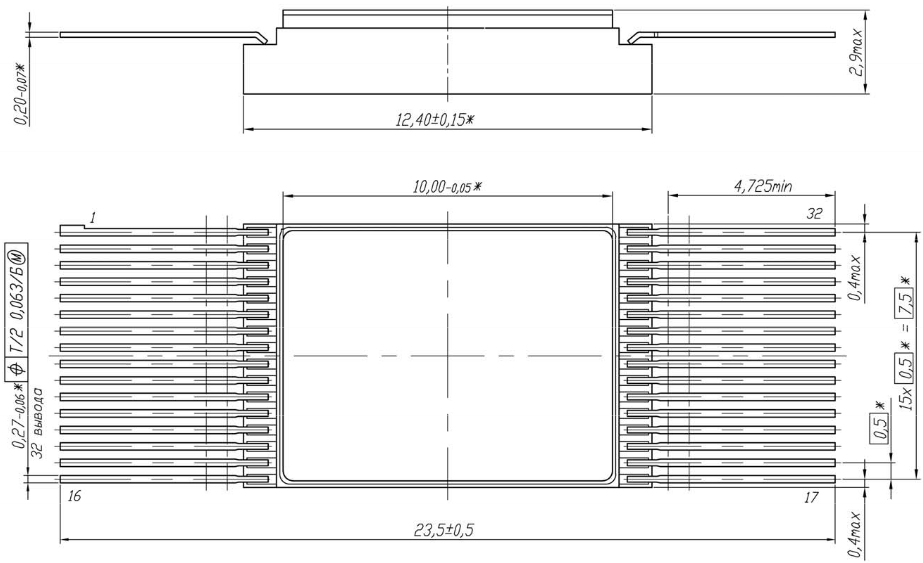

Габариты 1666РЕ014

Общий вид, габаритные, установочные и присоединительные размеры микросхемы 1666РЕ014 в корпусе 4184.32-1 приведены на рисунке 1. Корпус микросхемы металлокерамический, выводы покрыты золотом, вес микросхем не более 1,5 грамм.

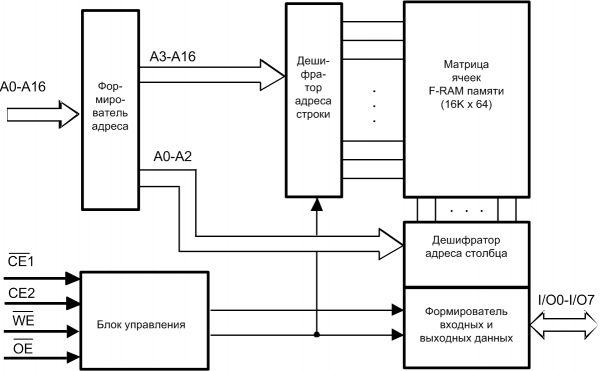

Структура и условное графическое обозначение 1666РЕ014

Структурная схема микросхемы 1666РЕ014 приведена на рисунке 2.

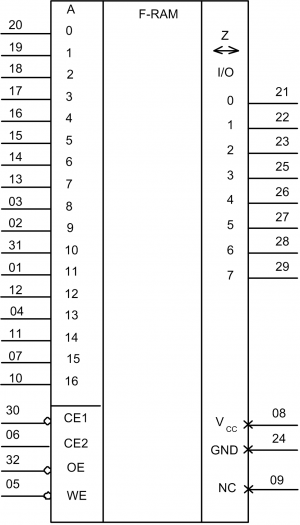

Условное графическое обозначение микросхемы представлено на рисунке 3.

Таблица истинности и назначение выводов микросхемы приведены в таблицах 3 и 4 соответственно.

Таблица 3 – Таблица истинности микросхемы 1666РЕ014

| Режим | Выводы | ||||||

|---|---|---|---|---|---|---|---|

Примечание:

H – высокий уровень напряжения;

L – низкий уровень напряжения;

Z – выход в состоянии «Выключено»;

X – любой уровень напряжения (низкий или высокий);

↑– фронт сигнала;

↓– спад сигнала.

1. Запись проводится по спаду сигналов CE1 или WE или фронту сигнала CE2 в зависимости от того, какой из сигналов будет первым.

2. Режим записи по WE начинается как режим чтения, во время которого происходит переключение адресов A16‑A3.

3. Адреса A2–A0 должны оставаться неизменными не менее 15 нс от начала режима записи.

Таблица 4 – Назначение выводов микросхемы 1666РЕ014

| Номер вывода | Обозначение вывода | Назначение вывода |

|---|---|---|

Описание режимов работы микросхемы

F-RAM матрица микросхемы организована в виде 16384 строк, каждая строка имеет 8 столбцовых ячеек (байтов), что позволяет реализовать быструю выборку при работе в страничном режиме. После того, как один раз зафиксирован начальный адрес по спаду CE1 (в то время как СЕ2 высокий) или по фронту СЕ2 (в то время как CE1 низкий), последующие ячейки столбцов доступны без необходимости переключения сигнала разрешения кристалла. В случае отключения любого вывода разрешения кристалла, начинается операция предустановки. Запись происходит непосредственно в конце выборки без задержки. Вывод WE1 должен переключаться при каждой операции записи.

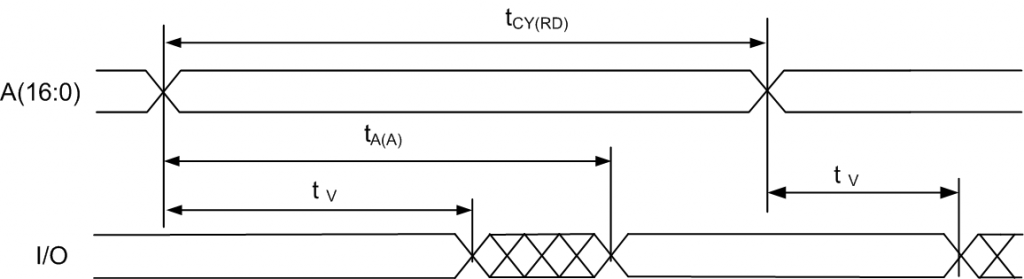

Операция чтения

Операция чтения начинается по спаду CE1 (в то время как СЕ2 высокий) или по фронту СЕ2 (в то время как CE1 низкий). CE – инициированная выборка вызывает защёлкивание адреса и начинает цикл чтения памяти, если WE высокий. Данные становятся доступными на шине после выполнения требований по времени выборки. После того, как адрес зафиксирован, и выборка завершена, может начинаться новая выборка по произвольному адресу (другая строка), пока оба разрешения кристалла ещё активные. Время минимального цикла для произвольного адреса равно tRC. В отличие от СОЗУ, CE – инициированное время выборки микросхемы быстрее, чем время адресного цикла.

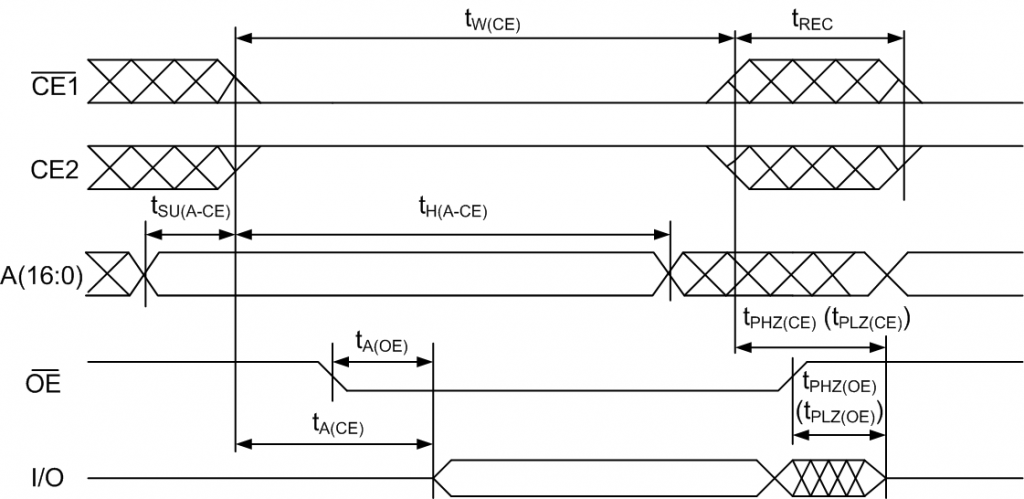

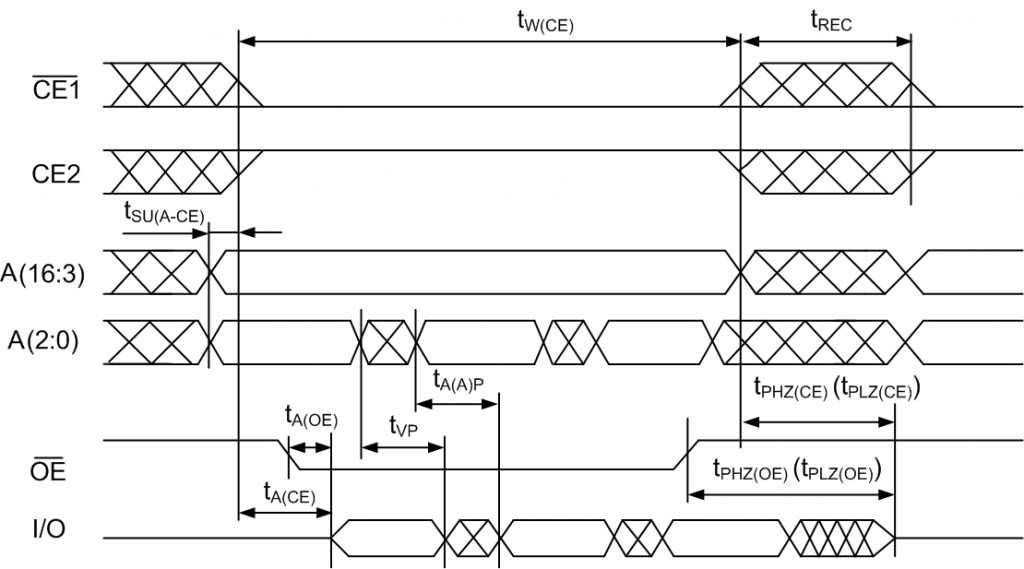

Микросхема будет управлять шиной данных только тогда, когда OE установлен низким и выполнено требование по времени выборки памяти. Если OE установлен перед завершением доступа к памяти, то шина данных не будет управляться, пока не будут доступными правильные данные. Это минимизирует ток потребления в системе, исключая переходные процессы, вызываемые передачей неправильных данных на шину. Диаграммы работы микросхемы в режимах чтения приведены на рисунках 4 и 5 соответственно.

Операция записи

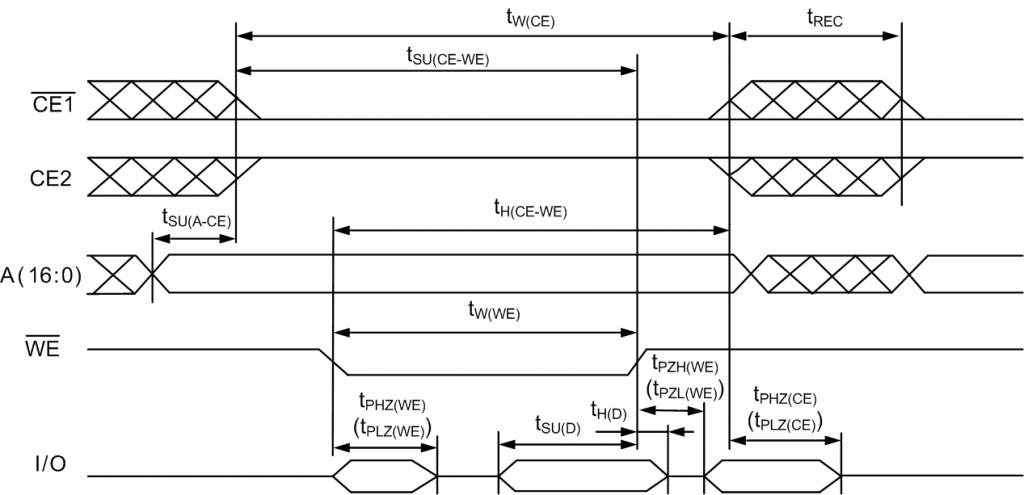

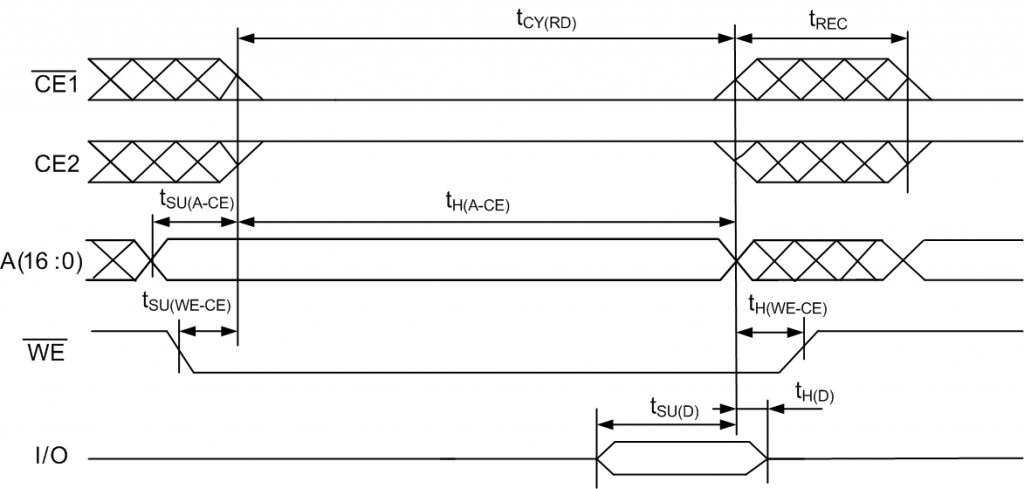

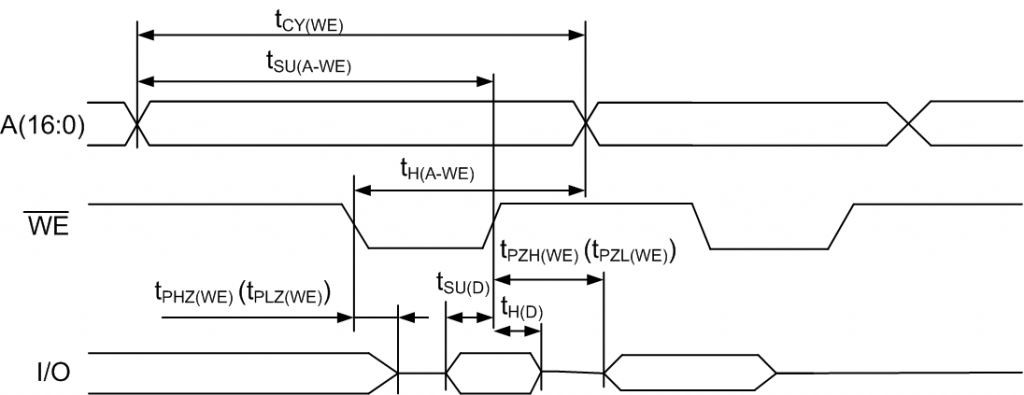

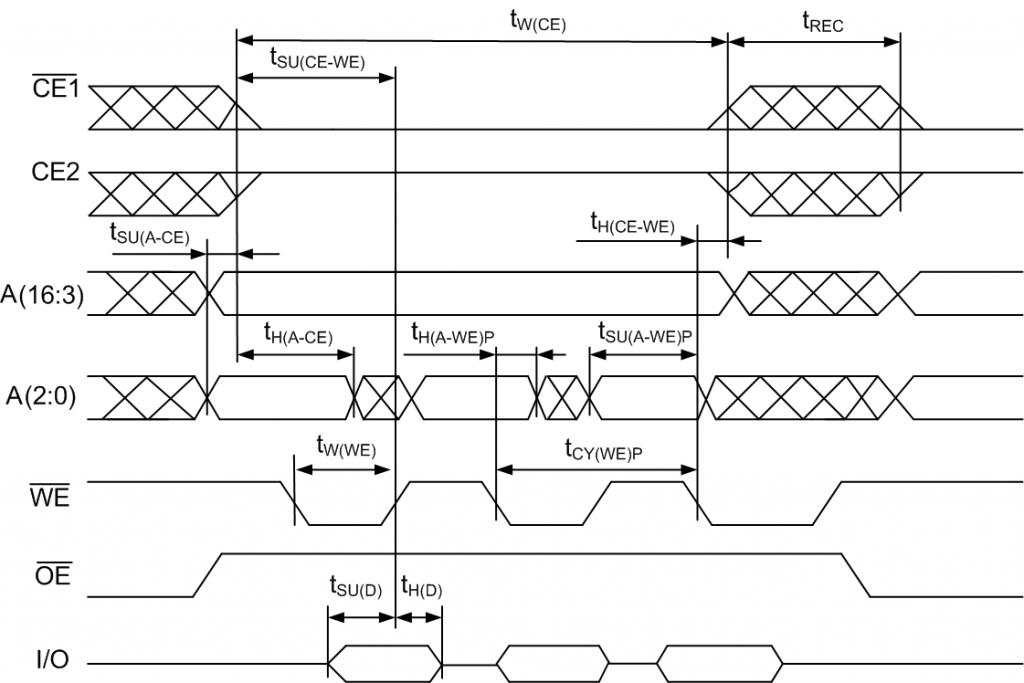

Микросхема поддерживает оба цикла записи с CE — и — WE управлением. В обоих случаях, адрес защёлкивается по спаду CE1 (в то время как СЕ2 высокий) или по фронту СЕ2 (в то время как CE1 низкий).

При записи с CE — управлением сигнал WE устанавливается перед началом цикла записи. Это означает, что WE является низким, когда микросхема активирована с помощью сигнала разрешения кристалла. В этом случае микросхема начинает цикл работы памяти как запись. Микросхема не будет управлять шиной данных независимо от состояния OE, пока WE является низким. При записи с WE — управлением цикл начинается, когда микросхема активируется посредством сигнала разрешения кристалла. Цикл памяти начинается как чтение. Шина данных будет управляться, если OE является низким, однако она будет в «третьем» состоянии, так как WE установлен низким.

Синхронизация записи с CE — и WE — управлением показаны на рисунках 6-8. На временной диаграмме цикла записи, приведенной на рисунке 7, шина данных показана как hi – Z состояние, пока кристалл разрешен для записи и перед требуемым временем предустановки. Хотя это состояние изображено как напряжение среднего уровня, рекомендуется, чтобы все I/O выводы выполняли требования по минимальным рабочим уровням UIH/UIL.

Доступ для записи в матрицу начинается по спаду WE после инициации цикла работы памяти. Доступ для записи завершается при снятии установок WE, CE1 или CE2, какая бы ни пришла первой. Правильная операция записи требует от пользователя выполнить технические требования по времени доступа перед снятием установок WE, CE1 или CE2. Время предустановки данных обозначает интервал, в течение которого данные не могут меняться до окончания доступа для записи.

В F-RAM нет задержки по записи. Поскольку времена доступа чтения и записи являются одинаковыми, пользователь не ощущает задержки по шине, работа всей памяти происходит в одном цикле шины. Диаграммы работы микросхемы в режимах записи показаны на рисунках 6, 7 и 8.

Работа в страничном режиме

Микросхема предоставляет пользователю быстрый доступ к любым данным в пределах строки. Каждая строка имеет восемь ячеек столбцов (байтов). Доступ может начаться в любом месте в пределах строки, и другие адреса ячеек столбцов могут быть доступными без необходимости переключать выводы СЕ. Для чтения в страничном режиме, как только первый байт данных отправлен на шину, входы адреса столбца А(2:0) могут быть изменены на новое значение. Новый байт данных затем будет отправлен на выводы I/O. Для записей в страничном режиме первый импульс записи определяет первый доступ записи. В то время как прибор выбран (установлены оба разрешения кристалла), последующий импульс записи совместно с новым адресом столбца обеспечивает доступ по записи в страничном режиме. Диаграммы работы микросхемы в режиме страничного чтения и записи приведены на рисунках 9 и 10 соответственно.

Операция предустановки

Операция предустановки является внутренним режимом, в котором состояние памяти подготавливается для нового доступа. Предустановка инициируется пользователем, переводя по меньшей мере один из сигналов разрешения кристалла в неактивное состояние. Разрешение кристалла должно оставаться неактивным в течение, минимального времени предустановки tPC.

Основные технические характеристики 1666РЕ014

Диапазон напряжения питания микросхем должен быть от 2,0 до 3,6 В. Основные электрические параметры микросхем при приемке и поставке приведены в таблице 5. Предельные и предельно-допустимые режимы эксплуатации приведены в таблице 6. Предельная температура p-n перехода кристалла 150 °С. Микросхема должны быть устойчива к воздействию статического электричества с потенциалом не менее 2000 В. Входная емкость микросхем не более 6,5 пФ, емкость входа/выхода микросхем не более 8,5 пФ при f = 1 МГц, UCC = 3,3 В. Количество циклов обращения N в нормальных условиях не менее 1014. Значение собственной резонансной частоты микросхем не менее 12 800 Гц. Тепловое сопротивление кристалл-корпус не более 8,9 °С/Вт.

Таблица 5 – Электрические параметры 1666РЕ014 при приемке и поставке

| Наименование параметра, единица измерения, режим измерения | Обозначение параметра | Норма параметра | Температура среды, °С |

|

|---|---|---|---|---|

| Выходное напряжение высокого уровня, В, при IOH = |-1,0| мА, UCC = 2,7 B | -60;125 |

|||

| Выходное напряжение высокого уровня, В, при IOH = |-100| мкА, UCC = 2,0 B | ||||

| Выходное напряжение низкого уровня, В, при IOL = 2,0 мА, UCC = 2,7 B | ||||

| Выходное напряжение низкого уровня, В, при IOL = 150 мкА, UCC = 2,0 B | ||||

| Ток утечки низкого уровня на входе (кроме СЕ2), мкА при UIL = 0 В | ||||

| Ток утечки высокого уровня на входе (кроме СЕ2), мкА при UIH = UCC | ||||

| Выходной ток низкого уровня в состоянии «Выключено», мкА при UO = 0 B | ||||

| Выходной ток высокого уровня в состоянии «Выключено», мкА при UO = UCC | ||||

| Ток потребления в режиме хранения, мкА при UCC = 3,6 В, UIL = 0,2 В, UIH = UCC – 0,2, UIL(CЕ2)1) = 0 В; UIH(CЕ1)2) = UCC | ||||

| Динамический ток потребления, мА при UCC = 3,6 В, UIL = 0,2 В, UIH = UCC – 0,2, tCY(RD) = 90 нс, IO = 0 А | ||||

| Входное сопротивление (по СЕ2), кОм, при UIH = 0,75·UCC | ||||

| Входное сопротивление (по СЕ2), МОм, при UIH = 0,25·UCC | ||||

| Количество циклов обращения | ||||

| Время цикла считывания, нс при 2,0 В ≤ UCC < 2,7 В | -60;125 |

|||

| Время цикла считывания, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время выборки адреса, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Время выборки адреса, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время выборки адреса в страничном режиме, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Время выборки адреса в страничном режиме, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время выбора, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Время выбора, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время выборки разрешения выхода, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Время выборки разрешения выхода, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время сохранения данных при смене адреса, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Время сохранения данных при смене адреса, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время сохранения данных при смене адреса в страничном режиме, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Время сохранения данных при смене адреса в страничном режиме, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время задержки распространения при переходе из состояния высокого, низкого уровня в состояние "Выключено.", нс, от входа CE1 (CE2) к выходам I/O при 2,0 В ≤ UCC < 2,7 В | tPLZ(CE)3) | |||

| Время задержки распространения при переходе из состояния высокого, низкого уровня в состояние "Выключено.", нс, от входа CE1 (CE2) к выходам I/O при 2,7 В ≤ UCC < 3,6 В | ||||

| Время задержки распространения при переходе из состояния высокого, низкого уровня в состояние "Выключено.", нс, от входа OE к выходам I/O при 2,0 В ≤ UCC < 2,7 В | tPLZ(OE)3) | |||

| Время задержки распространения при переходе из состояния высокого, низкого уровня в состояние "Выключено.", нс, от входа OE к выходам I/O при 2,7 В ≤ UCC < 3,6 В | ||||

| Время цикла записи, нс при 2,0 В ≤ UCC < 2,7 В | -60;125 |

|||

| Время цикла записи, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время цикла записи в страничном режиме, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Время цикла записи в страничном режиме, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время установления сигнала разрешения относительно окончания сигнала записи, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Время установления сигнала разрешения относительно окончания сигнала записи, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время удержания сигнала разрешения относительно сигнала записи, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Время удержания сигнала разрешения относительно сигнала записи, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Длительность сигнала записи, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Длительность сигнала записи, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время установления адреса относительно окончания сигнала записи, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Время установления адреса относительно окончания сигнала записи, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время установления адреса относительно сигнала записи в страничном режиме, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Время установления адреса относительно сигнала записи в страничном режиме, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время удержания адреса относительно сигнала записи, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Время удержания адреса относительно сигнала записи, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время удержания адреса относительно сигнала записи в страничном режиме, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Время удержания адреса относительно сигнала записи в страничном режиме, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время установления данных относительно окончания записи, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Время установления данных относительно окончания записи, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время удержания данных относительно окончания записи, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Время удержания данных относительно окончания записи, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время восстановления, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Время восстановления, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время установления адреса относительно сигнала разрешения, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Время установления адреса относительно сигнала разрешения, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время удержания адреса относительно сигнала разрешения, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Время удержания адреса относительно сигнала разрешения, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Длительность сигнала разрешения, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Длительность сигнала разрешения, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время установления сигнала записи относительно сигнала разрешения, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Время установления сигнала записи относительно сигнала разрешения, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время удержания сигнала записи относительно сигнала разрешения, нс при 2,0 В ≤ UCC < 2,7 В | ||||

| Время удержания сигнала записи относительно сигнала разрешения, нс при 2,7 В ≤ UCC < 3,6 В | ||||

| Время задержки распространения при переходе из состояния высокого, низкого уровня в состояние "Выключено.", нс, от входа WE к выходам I/O (при СL = 5 пФ), при 2,0 В ≤ UCC < 2,7 В | tPZL(WE)3) | |||

| Время задержки распространения при переходе из состояния высокого, низкого уровня в состояние "Выключено.", нс, от входа WE к выходам I/O (при СL = 5 пФ), при 2,7 В ≤ UCC < 3,6 В | ||||

| Время задержки распространения при переходе из состояния высокого, низкого уровня в состояние "Выключено.", нс, от входа WE к выходам I/O (при СL = 5 пФ), при 2,0 В ≤ UCC < 2,7 В | tPLZ(OE)3) | |||

| Время задержки распространения при переходе из состояния высокого, низкого уровня в состояние "Выключено.", нс, от входа WE к выходам I/O (при СL = 5 пФ), при 2,7 В ≤ UCC < 3,6 В | ||||

Примечание:

1. UIL(CЕ2) – входное напряжение низкого уровня на выводе СЕ2.

2. UIH(CЕ1) – входное напряжение высокого уровня на выводе CE1.

3. Динамические параметры tPHZ(CE), tPLZ(CE), tPHZ(OE), tPLZ(OE), tPZH(WE), tPZL(WE), tPHZ(WE), tPLZ(WE), tSU(WE-CE), tH(WE-CE) не контролируются, так как их значения обеспечиваются проведением функционального контроля на максимальной частоте.

4. Соотношение между CE1 (CE2) и WE определяется, если запись происходит под контролем CE1 (CE2) и WE.

Таблица 6 – Предельно-допустимые и предельные режимы эксплуатации 1666РЕ014

| Наименование параметра | Буквенное обозначение | Предельно- допустимый режим | Предельный режим |

||

|---|---|---|---|---|---|

| Напряжение питания, В | |||||

| Входное напряжение низкого уровня, В | |||||

| Входное напряжение высокого уровня, В | |||||

| Выходной ток высокого уровня, мА | |||||

| Выходной ток низкого уровня, мА | |||||

| Длительность фронта/спада входного сигнала, нс | |||||

| Емкость нагрузки, пФ | |||||

Примечание:

1. UIH < UCC + 1 В.

2. Допускается эксплуатация микросхемы при длительности фронта, спада входного сигнала до 200 нс. Динамические параметры микросхемы tLH, tHL > 3 нс не регламентируются.

3. Допускается эксплуатация микросхемы при емкости нагрузки до 200 пФ. Динамические параметры микросхемы при CL > 30 пФ не регламентируются.

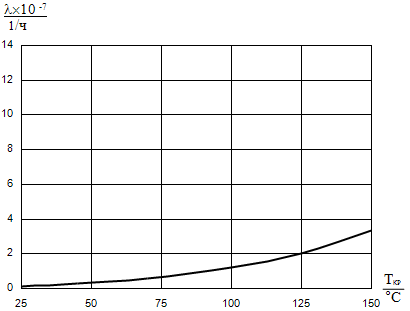

Надежность микросхемы 1666РЕ014

Наработка до отказа в режимах и условиях эксплуатации, допускаемых ТУ, при температуре окружающей среды не более (65 + 5) °С должна быть не менее 100000 ч и не менее 120000 ч в следующем облегченном режиме: напряжение питания микросхем UCC = (2,1 ÷ 2,6) B, выходной ток IOH = |-50| мкА, IOL = 75 мкА и UCC = (2,8 ÷ 3,4) В, выходной ток IOH = |-0,5| мА, IOL = 1,0 мА.

Указания по применению и эксплуатации микросхемы 1666РЕ014

Прогнозируемая зависимость интенсивности отказов от температуры кристалла приведена на рисунке 11.

При ремонте аппаратуры и измерении параметров микросхемы в контактирующих устройствах замену микросхемы необходимо проводить только при отключенных источниках питания.

Запрещается непосредственное подведение каких-либо сигналов (в том числе шин UCC и GND) к корпусу, к выводам микросхемы, неиспользуемым согласно электрической схеме микросхемы.

Порядок подачи напряжений питания и входных сигналов на микросхему должен быть последовательным: подача нулевого потенциала на общий вывод микросхемы, подача напряжения на вывод питания, подключение выводов микросхемы в соответствии с необходимым режимом работы микросхемы, или одновременным.

Снятие напряжений питания и входных сигналов на микросхему производить в обратном порядке или одновременно.

Не допускается подача входных сигналов на микросхему при отключенном источнике питания.

Рекомендуется вывод UCC каждой микросхемы соединять с выводом GND через конденсатор емкостью 0,1 мкФ ± 10 %.

Динамический ток потребления при работе микросхемы IOCC(R), А, рассчитывается по формуле:

где IOCC – норма динамического тока потребления в соответствии с техническими условиями, А;

N – число выходов микросхемы;

CLi – емкость нагрузки i-го выхода, Ф;

UCC – напряжение питания, В;

fi – частота переключения i-го выхода, Гц.

Внешние воздействующие факторы

Механические воздействия по ОСТ В 11 0998. Климатические факторы по ОСТ В 11 0998. Требования по устойчивости к воздействию статической пыли не предъявляются.

Микросхема 1666РЕ014 должна быть устойчива к воздействию специальных факторов с характеристиками:

– 7.И1 по группе исполнения 4Ус;

– 7.И6 по группе исполнения 0,5×5Ус;

– 7.И7 по группе исполнения 4Ус;

– 7.С1 по группе исполнения1Ус;

– 7.С4 по группе исполнения 0,5×1Ус;

– 7.К1 по группе исполнения 0,25×2К (поток электронов: 50 крад);

– 7.К4 по группе исполнения 0,25×1К (поток протонов: 50 крад).

Требования к специальным факторам с характеристиками 7.И4, 7.И10, 7.И11, 7.К3, 7.К6, 7.К9, 7.К10, 7.К11, 7.К12 не предъявляются.

Допускается в процессе и непосредственно после воздействия специальных факторов с характеристикой 7.И6 временная потеря работоспособности микросхемы. По истечении 40 мс от начала воздействия работоспособность восстанавливается.

Уровень бессбойной работы (7.И8) при воздействии специального фактора с характеристикой 7И6 не хуже 0,001×1УС (1Ус в режиме хранения информации при UCC от 0 до 3,6 В).

Критериями работоспособности являются UOL1, UOL2, UOH1, UOH2, ICCS, функционирование.

Микросхемы должны обладать электрической прочностью к воздействию одиночных импульсов напряжения, возникающих при воздействии ЭМИ.

Микросхемы обладают стойкостью к воздействию одиночных импульсов напряжения (импульсной электрической прочностью). Фактические значения предельно-допустимого одиночного импульсного напряжения (ОИН) приведены в таблице 7.

Таблица 7 – Значения предельно-допустимого ОИН

| Тип вывода | Предельно-допустимое напряжение одиночного импульса (В) в зависимости от длительности импульса |

|---|---|

| |

|

| Входы | |

| Выходы | |

| Цепь питания |

Расчетные значения предельно-допустимой энергии представлены в таблице 8.

Таблица 8 – Расчетные значения предельно-допустимого энергии

| Тип вывода | Расчетная предельно-допустимая энергия ОИН (в мДж) в зависимости от длительности ОИН (в мкс) |

|---|---|

| Входы | |

| Выходы | |

| Цепь питания |

Преимущества:

1. Микросхема 1666РЕ014 является отечественной разработкой с известными параметрами радиационной стойкости и надежности, что позволяет применять микросхему в разработках электронной техники специального назначения и отказаться от использования некоторых микросхем памяти иностранного производства. При этом значительно сокращая стоимость закупки (в случае применения ЭКБ с уровнем качества space, military) и сроки поставки или затраты на проведение сертификационных испытаний (в случае применения ЭКБ с уровнем качества industrial).

2. Микросхема 1666РЕ014 имеет расширенный диапазон напряжения питания (2,0 ÷ 3,6 В), что расширяет область применения ее в схемах как с 2,5 В так и 3,3 В питанием.

3. Микросхема 1666РЕ014 конструктивно выполнена в достаточно компактном корпусе 4184.32-1, занимаемая площадь под микросхемой на печатной плате составляет всего 112 мм2 (размеры: 8 мм × 14 мм).

4. Крайне низкое энергопотребление в режиме чтения/запись по сравнению с обычными СОЗУ (1645РУ1А(Б, В)У хранение → 5 мА, запись → 60 ÷ 120 мА) или ЭСППЗУ (1636РР51У хранение → 1 мА, запись → 40 мА).

5. Количество циклов чтения/запись достигает 1 триллиона при температуре эксплуатации 125 °С и 100 триллионов при эксплуатации в нормальных климатических условиях, против микросхем памяти выполненных по технологиям NOR или NAND Flash.

6. Микросхема 1666РЕ014 особенно актуальна для применения в составе электронных блоков космических систем, так как является радиационно стойкой (поток протонов: 50 крад, поток электронов: 50 крад). Данная микросхема может найти свое применение в различных бортовых вычислительных системах в качестве памяти данных и программ.

Хотелось бы:

1. Сравнительно не большой объем памяти, но для определенных задач вполне достаточный. Для будущих разработок хотелось бы 2 Мбит или например столько.

2. К сожалению микросхема 1666РЕ014 не проходила испытания на стойкость к воздействию высокоэнергетичных протонов (ВЭП) и тяжелых заряженных частиц (ТЗЧ), характеристики 7К9, 7К10, 7К11 и 7К12, так как данные требования на этапе проектирования к микросхеме не предъявлялись.

Спасибо за информацию